Standard veröffentlicht: HBM4 ist fertig und noch etwas schneller geworden

Jetzt sind sie final, die Spezifikationen für die neue Generation des High Bandwidth Memory. Die JEDEC-Richtlinien sehen für HBM4 einen Durchsatz von 8 Gbit/s pro Pin und somit 2 TB/s pro Speicherstapel mit 2.048-Bit-Interface vor. Das ist sogar noch mehr als eingangs genannt wurde.

Im vergangenen Sommer hatte die JEDEC, deren Mitglieder aus Herstellern der Halbleiterbranche stammen, nämlich zunächst 6,4 Gbit/s pro Pin als vorläufiges Maximum für HBM4 genannt. Allerdings war auch bereits von anhaltenden Verhandlungen über höhere Geschwindigkeiten die Rede, die nun mit den finalen Spezifikationen Früchte tragen.

HBM4 ermöglicht 2 TB/s Datendurchsatz pro Stack

Der Durchsatz von 8,0 Gbit/s pro Pin ist zwar nur wenig mehr als bei HBM3 mit 6,4 Gbit/s, doch bei HBM4 fällt der Speicherbus mit 2.048 Bit doppelt so breit aus, sodass am Ende mehr als eine Verdoppelung der maximalen Durchsatzrate erfolgt. Sind es bei HBM3 nach JEDEC-Norm noch bis zu 819 GB/s pro Stapel (Stack), wurden für HBM4 nun 2.048 GB/s oder 2 TB/s definiert.

| Interface | max. Durchsatz pro Pin | max. Durchsatz pro Stack | |

|---|---|---|---|

| HBM1 (JEDEC) | 1.024 Bit | 1,0 Gb/s | 128 GB/s |

| HBM2 (JEDEC) | 2,0 Gb/s | 256 GB/s | |

| HBM2E | 3,6 Gb/s | 461 GB/s | |

| HBM3 (JEDEC) | 6,4 Gb/s | 819 GB/s | |

| HBM3E (Micron) | 9,2 Gb/s | 1.178 GB/s | |

| HBM3E (Samsung) | 9,8 Gb/s | 1.254 GB/s | |

| HBM3E (SK Hynix) | 10,0 Gb/s | 1.280 GB/s | |

| HBM4 (JEDEC) | 2.048 Bit | 8,0 Gb/s | 2.048 GB/s |

| HBM4E | ~10,0 Gb/s | ~2.560 GB/s |

HBM4E wird noch schneller

Wie in der Vergangenheit werden Hersteller später mit HBM4E ein eigenes Süppchen kochen und die maximalen Übertragungsraten noch weiter steigern. Samsung hatte jüngst auf der GTC 2025 schon Pläne für HBM4E mit 10 Gbit/s geäußert. Damit wären rund 2,5 TB/s pro Stack möglich.

Stapelgrößen wie gehabt

HBM ist eine spezielle Variante von DRAM. Genauer gesagt besteht HBM aus übereinander gestapelten DRAM-Dies. Das erlaubt hohe Speicherkapazitäten auf kleiner Fläche und sorgt dank des breiten Speicherbus auf einem Interposer in unmittelbarer Nähe zum Prozessor auch für enorme Transferraten.

Für HBM4 sind Stapel mit 4, 8, 12 oder 16 DRAM-Dies definiert, die via Silizium-Durchkontaktierung (TSV) miteinander verbunden sind. Auf Basis der 3-GByte-Dies (24 Gbit) sind so Stapel mit 12 GByte, 24 GByte, 36 GByte und 48 GByte möglich. Mit den neuen 4-GByte-Dies (32 Gbit) könnten die HBM4-Stapel entsprechend 16 GByte, 32 GByte, 48 GByte und 64 GByte fassen. In puncto maximaler Speicherkapazität ändert sich gegenüber HBM3 also nichts. HBM3 mit 16 Ebenen ist bisher aber nicht erhältlich, das könnte bei HBM4(E) geschehen.

Flexiblere Spannungen und Rowhammer-Schutz

Mehr Flexibilität bei der elektrischen Spannung soll Vorteile bei Leistungsaufnahme und Energieeffizienz gegenüber HBM3 ermöglichen. Zudem gibt es mit Directed Refresh Management (DRFM) eine Sicherheitsmaßnahme gegen Rowhammer-Attacken.

Abwärtskompatibel zu HBM3

Obwohl sich die Zahl der Kontakte und Speicherkanäle (32) verdoppelt, ist HBM4 zum Vorgänger HBM3 kompatibel. Es können also ältere HBM3-Controller mit HBM4 kombiniert werden oder HBM3 und HBM4 im Mischbetrieb mit einem Controller eingesetzt werden, heißt es in der Pressemitteilung der JEDEC.

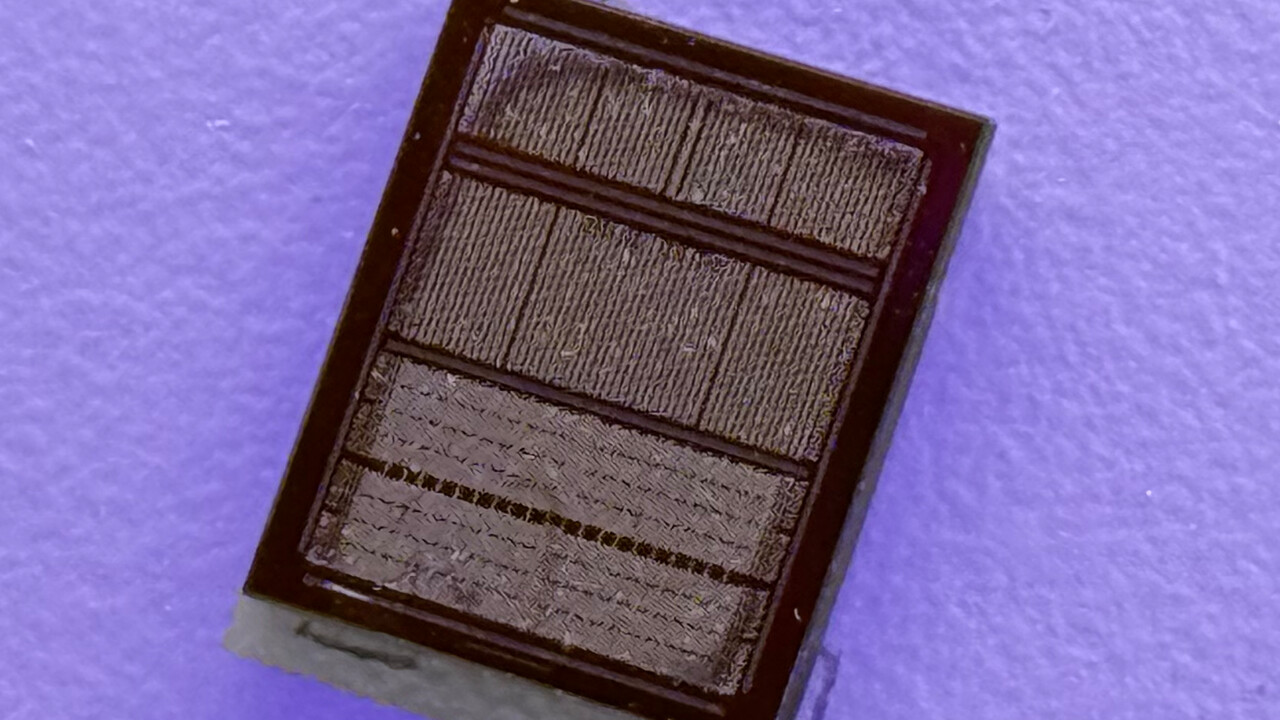

Erste HBM4-Chips werden bemustert

SK Hynix schreitet als HBM-Marktführer auch bei HBM4 vorne weg und hatte letzten Monat als erster Hersteller die Verfügbarkeit von Musterchips angekündigt. Dabei handelt es sich um 12-Layer-Modelle mit bisher nicht genannter Durchsatzrate und Kapazität.

Natürlich steht HBM4 auch bei Samsung und Micron auf der Roadmap. Nvidia will nächstes Jahr seine GPU-basierten Rechenbeschleuniger der Rubin-Generation mit HBM4 bestücken. AMD wird es voraussichtlich bei der Produktfamilie Instinct MI400 gleichtun und ebenfalls ab 2026 auf HBM4 setzen.