Speicherforschung: SK Hynix über 5-Bit-NAND, 3D FeNAND und die fertige CTI-Technologie

Im Dezember hat SK Hynix auf dem International Electron Devices Meeting (IEDM) über Forschungsprojekte im Bereich NAND-Flash referiert. Dazu zählt die Multi-Site-Cell-Technik mit Potenzial für 5 Bit pro Zelle sowie der effiziente 3D FeNAND, der möglichst viele TOPS/Watt liefern soll. Schon nahezu marktreif ist die CTI-Technik.

Forschung an 5-Bit-NAND (PLC) geht weiter

Auch wenn Solidigm schon vor Jahren eine erste Vorserien-SSD mit 5 Bit pro Speicherzelle (Penta-Level Cell, kurz PLC) gezeigt hatte, ist die Branche offensichtlich noch weit davon entfernt, daraus ein Massenprodukt zu machen.

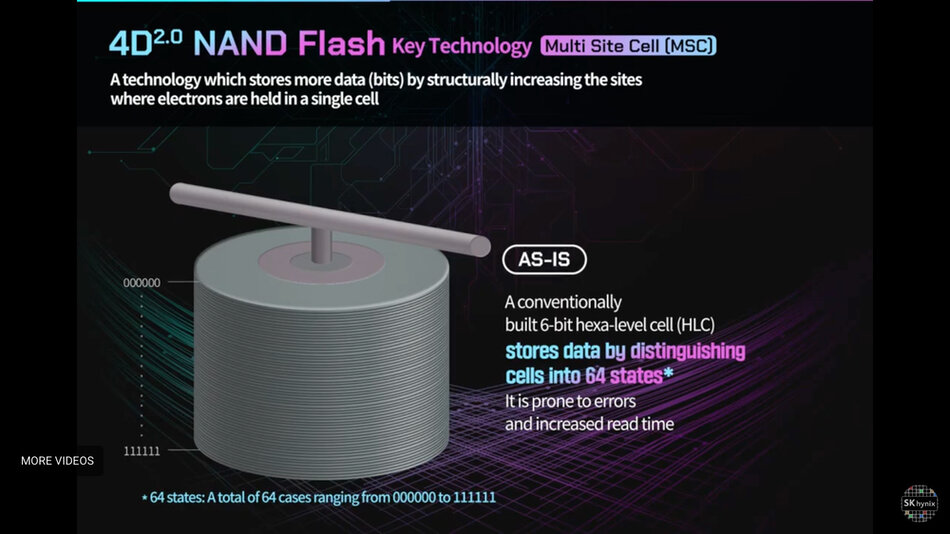

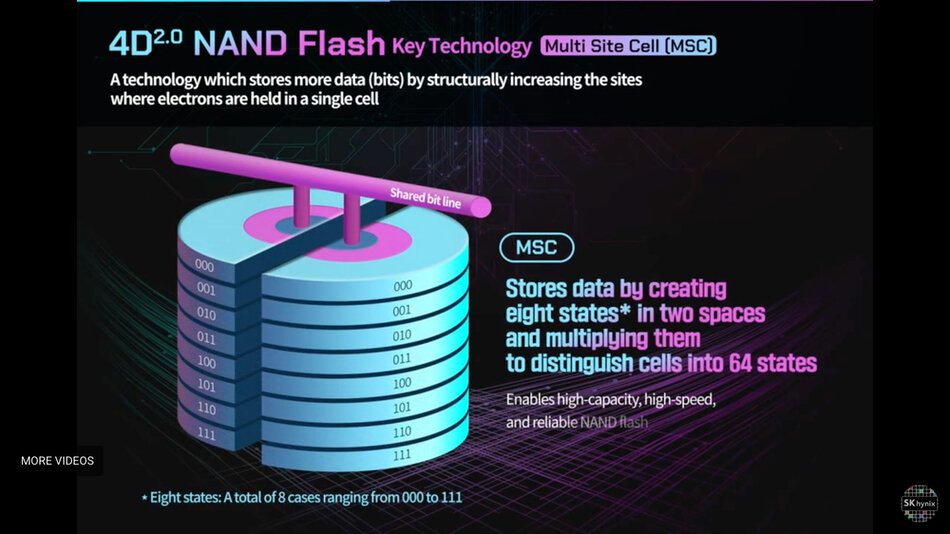

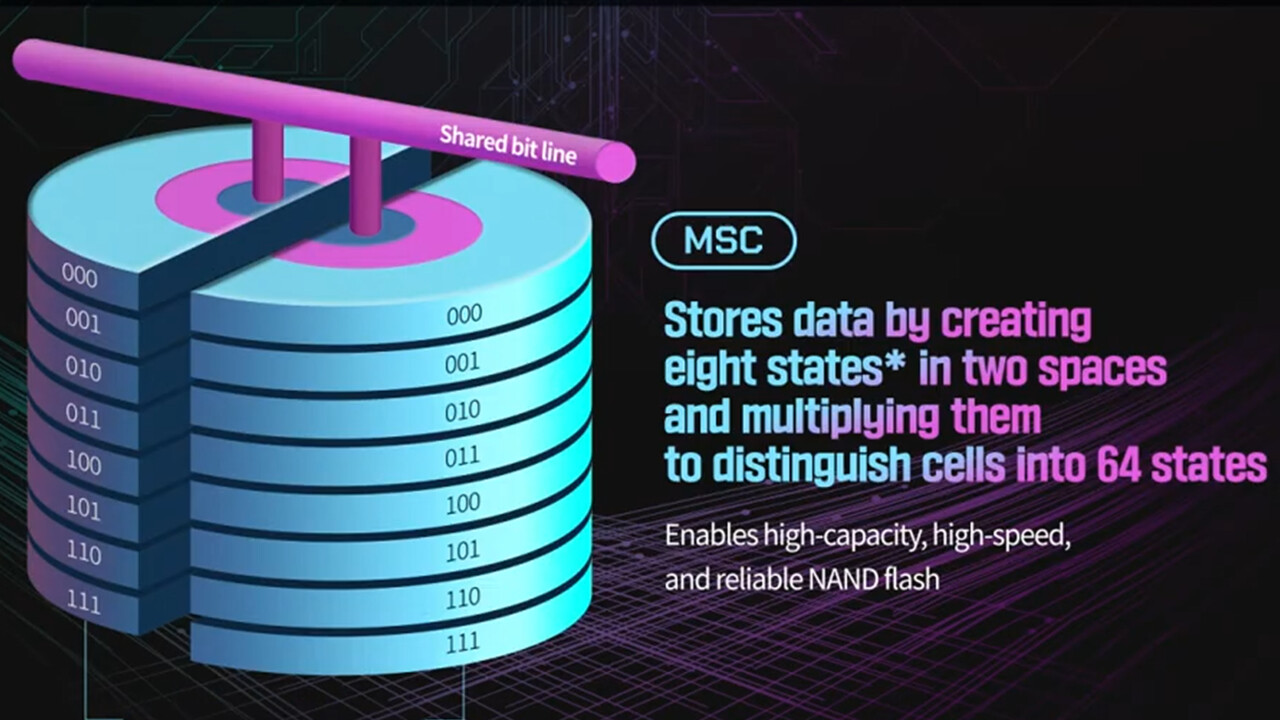

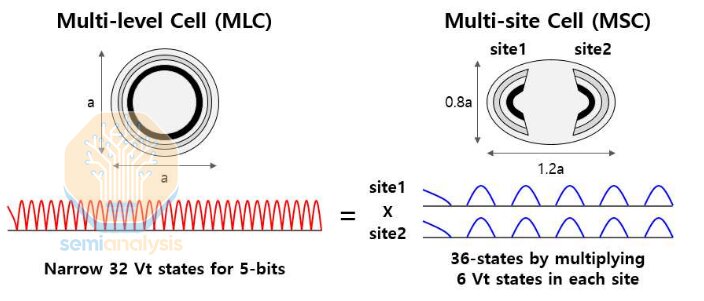

Kioxia (früher Toshiba Memory) forscht ebenfalls daran und hatte bereits 2019 das Konzept der halbierten Speicherzellen als „Twin BiCS Flash“ vorgestellt. Damit sollen sich 5 Bit pro Zelle besser realisieren lassen. Genau das verfolgt auch SK Hynix mit seinen 2022 vorgestellten „Multi-Site Cells“ (MSC). Auch hier wird des herkömmliche Design aufgespalten, sodass aus einer Zelle effektiv zwei entstehen und so aus 3 Bit pro Zelle sogar 6 Bit pro Zelle möglich werden – Stichwort Hexa-Level Cell, kurz HLC.

Zunächst will aber auch SK Hynix über ein solches Zellendesign NAND-Flash mit 5 Bit pro Zelle realisieren. Statt der normal dafür nötigen insgesamt 32 unterschiedlichen Spannungszustände werden laut der jüngsten Präsentation zur IEDM 2025 lediglich 6 verschiedene Spannungszustände benötigt. Diese werden durch das MSC-Design auf 36 multipliziert, sodass am Ende sogar einige ungenutzt übrig bleiben.

Die Website Blocks and Files berichtet, dass SK Hynix bereits funktionsfähige Chips gefertigt hat. Allerdings müsse noch ergründet werden, wie sich dieser PLC-NAND kosteneffizient in Serie produzieren lässt.

3D FeNAND für viel mehr TOPS/Watt

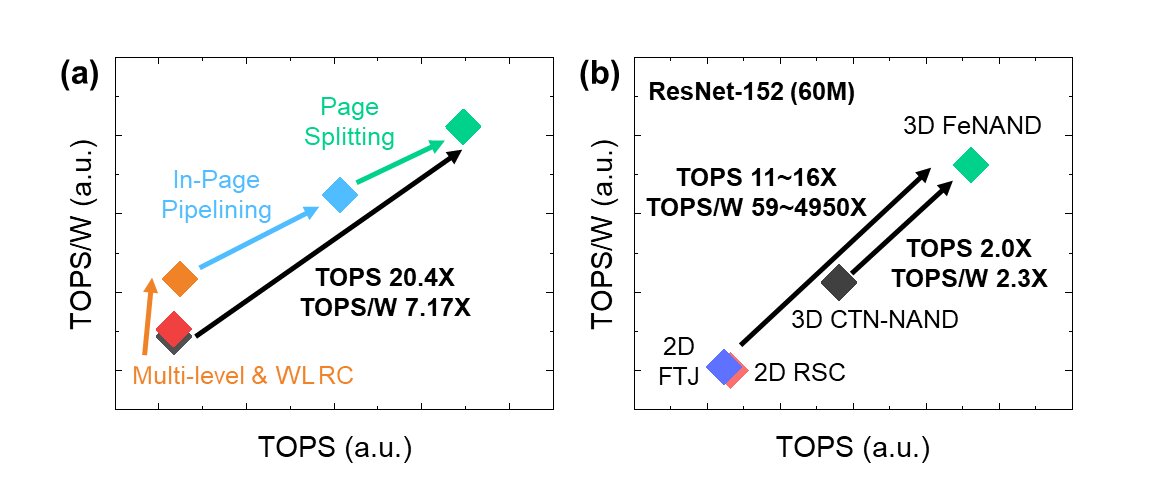

Ein weiteres Forschungsfeld ist der sogenannte Ferroelektrische NAND (FeNAND). Dieser ist laut einer Publikation von SK Hynix von Ende Dezember vor allem für In-Memory-Computing interessant und soll hohen Durchsatz mit geringem Energiebedarf kombinieren. Mit dem 3D FeNAND sollen die TOPS/Watt massiv steigen.

Auch in diesem Forschungsbereich ist SK Hynix nicht allein unterwegs. Samsung hatte erst Ende November eine Arbeit veröffentlicht, in der es um ferroelektrische Transistoren für NAND-Flash-Speicher mit geringer Leistungsaufnahme geht.

Bei Samsung geht dies aber auch in Richtung der 5 Bit pro Zelle, die mit den sparsamen FeFETs ebenfalls möglich wären.

Schon einsatzbereit: CTI-Technik für stabilere Zellen

Während die oben genannten Techniken noch Zukunftsmusik sind, ist SK Hynix bei einer anderen schon viel weiter, die aber auch kein radikal neues Zellendesign erfordert. Gemeint ist die sogenannte Charge-Trap-Nitrid-Isolation (CTI)-Technologie. Damit soll die Verteilung der Schwellenspannungen innerhalb der NAND-Zelle verbessert werden. Das wiederum sorge für besseren Datenerhalt und schnellere Lesezugriffe. Nach eigenen Angaben des Herstellers könne man bereits voll funktionsfähige Chips mit CTI-Technologie herstellen. Umgesetzt wurde dies zunächst in den Prozess zur Herstellung von 176-Layer-NAND.