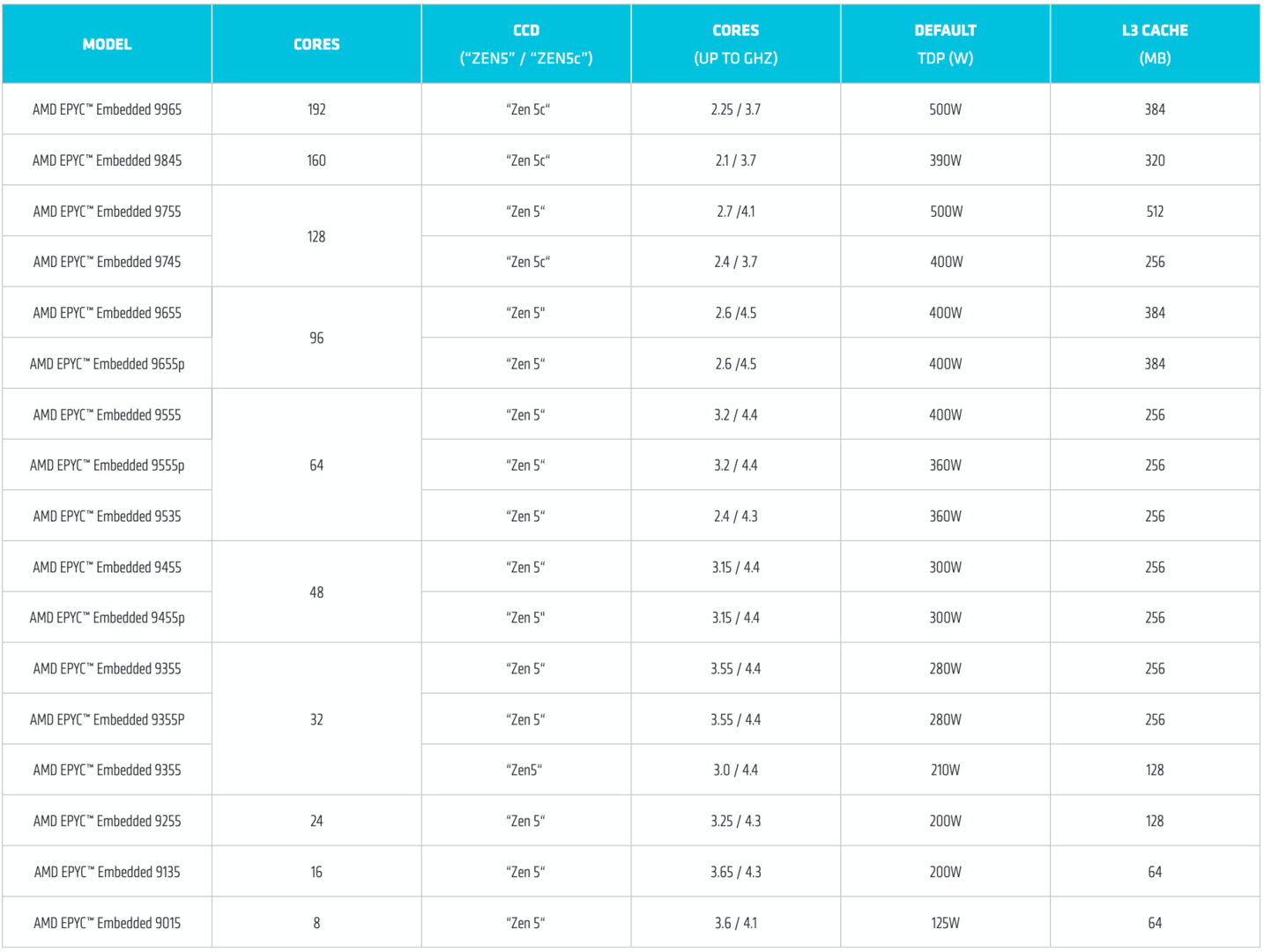

AMD Epyc Embedded 9005: 8 bis 192 Zen-5(c)-Kerne für weitere Industriezweige

Zur Embedded World 2025 bringt AMD neue Epyc-Prozessoren mit, die 8 bis 192 Zen-5(c)-Kerne in weitere Bereiche der Industrie platzieren. Wie in den Generationen zuvor wird dabei eine möglichst breite Übereinstimmung mit den regulären Modellen gesucht, im zweiten Quartal soll dann die Auslieferung der Epyc Embedded 9005 starten.

Embedded steht aber auch für lange Laufzeiten. Statt bisher fünf Jahre Support für die großen Epycs bereitzustellen, folgt AMD mit den Epyc Embedded 9005, Codename Turin, nun dem Industriestandard von mindestens sieben Jahren. Genutzt wird dafür weiterhin der Sockel SP5, der bereits mit dem Vorgänger Epyc (Embedded) 9004, Codename Genoa, eingeführt wurde. Zusammen mit den Neuvorstellungen steht diesem ein Leben von über einer Dekade nichts im Weg. Cisco und IBM werden die ersten Firmen sein, die AMD Epyc Embedded 9005 in größerem Stil nutzen werden, erklärt AMD.

Auf den ersten Blick sieht der große Server wie ein klassisches Produkt aus dem Datacenter aus. Das ist in einigen Gebieten auch durchaus der Fall, erklärte AMD, wenngleich es vielfältigere Einsatzgebiete gibt, die auch kleine Single-Slot-Systeme oder angepasste Dual-Sockel-Lösungen auf passenden Boards einschließen.

Obwohl das neue Aufgebot nach vielen Modellen aussieht, die AMD bereits im Portfolio hat, gibt es durchaus Anpassungen. So fehlen unter den neuen Embedded-Prozessoren die Varianten mit höchstem Takt, auf die maximale Anzahl von Kernen verzichtet AMD aber nicht. Im Gespräch mit ComputerBase auf der Embedded World 2025 erklärte der Hersteller, dass es dafür durchaus einen Markt gebe, unter anderem im Storage-Umfeld oder bei großen Firewall-Support-Systemen. Zusätzliche Features, die beispielsweise bei einem Stromausfall die Daten schnell zwischen DRAM und NVMe-SSDs hin- und herschieben können, gibt es laut Hersteller nur in AMDs Embedded-Segment.

AMD bestätigte, dass man die Modelle anpasse, wenn ein großer Kunde dies verlangt. Dabei wird primär aber nicht die Anzahl der Kerne geändert, sondern der Taktspielraum vergrößert oder verkleinert und dazu passend die TDP angepasst, erklärte AMD.

Die Grundausstattung bringen die Epyc-Prozessoren über die aus dem Datacenter bekannte SP5-Plattform alle mit: bis zu 160 PCIe Lanes, 12-Kanal-Speicher mit maximal 6.000 MT/s, wahlweise auch in einer Größe von bis zu 6 TByte pro Sockel.