CoWoP-Packaging: Neues Verfahren bei Nvidia Blackwell und Rubin im Testlauf

Bilder einer Nvidia-Roadmap offenbaren kommende Tests bevorstehender Rubin-Chips im ganz neuen CoWoP-Packaging-Verfahren. CoWoS läuft aber parallel weiter, sodass der Rubin-Chip als kommende Nvidia-Lösung nicht Gefahr läuft, bei Problemen mit dem neuen Packaging auf der Strecke zu bleiben.

CoWoP ist plötzlich in aller Munde. Denn es bekommt aufgrund durchgesickerter Nvidia-Folien plötzlich eine viel größere Bühne, sodass sich nun auch Analysten, Mainstream-Medien und die Börse zum Teil damit befassen.

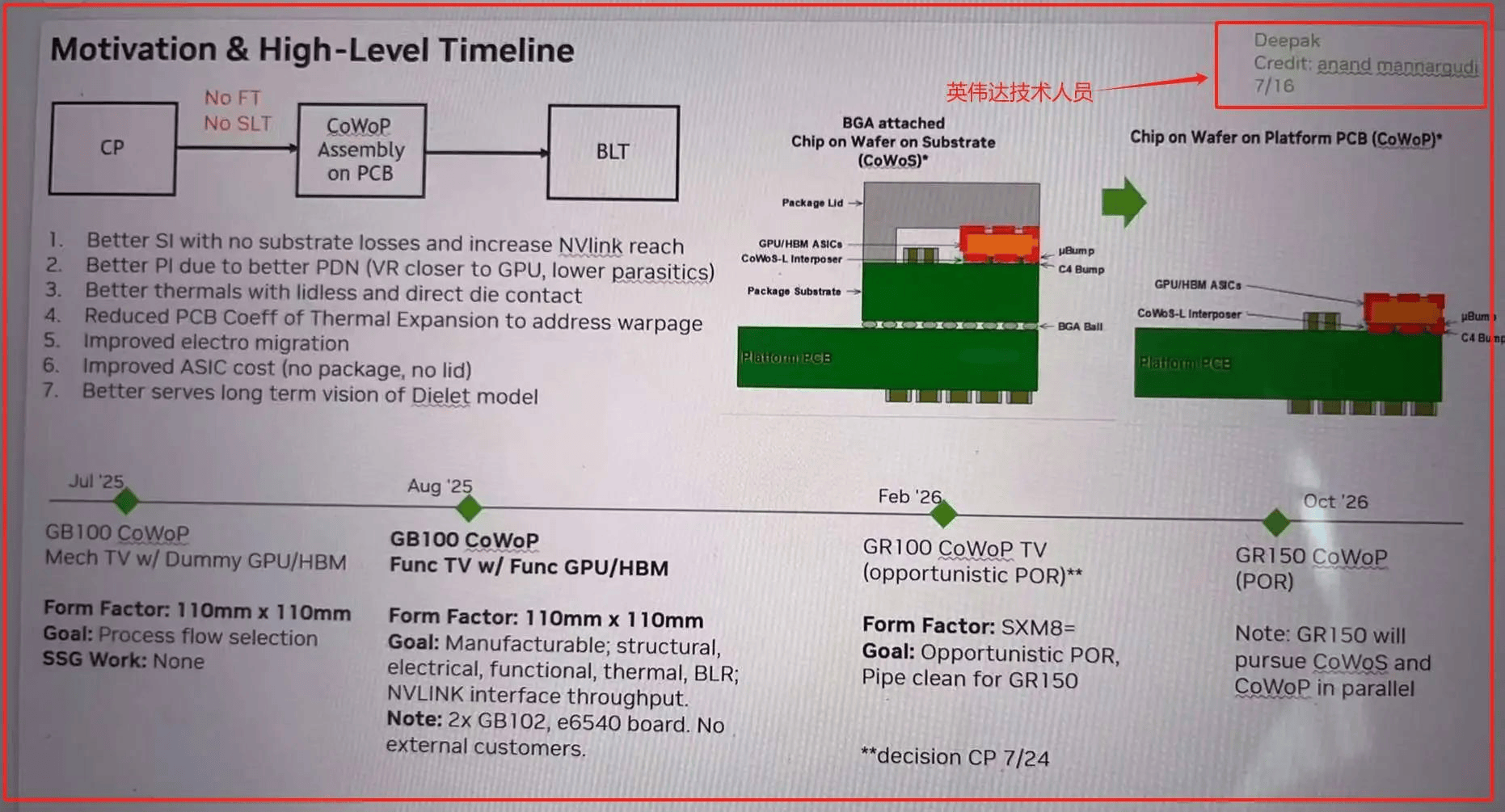

CoWoP steht für Chips on Wafer on Platform (PCB). Es ist eine mögliche Weiterentwicklung von CoWoS, Chips on Wafer on Substrat. Letzteres ist das aktuell genutzte Verfahren für das Packaging verschiedener Chips, wie multiplen GPU-Dies und HBM auf ein Substrat und dann zu einem Package, wie es bei großen AI-Beschleunigern die Regel ist. CoWoP ist dabei ein ziemlich radikaler Ansatz, er würde die meisten mittleren Schritte entfernen und die Chips letztlich fast direkt auf das PCB setzen.

Nvidia verfolgt diesen Ansatz, da sich das Unternehmen für die Zukunft diverse Vorteile davon verspricht. Diese reichen von besserer Signalqualität für höhere Datenraten über eine verbesserte Wärmeabfuhr für höhere TDPs bis hin zu geringeren Kosten, da die Interposer-Schritte entfallen würden. Aber es gibt auch Nachteile, die PCB-Fertigung wird deutlich komplexer, Nacharbeiten werden schwieriger und das passende Packaging-System mit allen Testverfahren müsste erst einmal aufgebaut werden.

Einen Zeitplan für die Tests hat Nvidia deshalb auch dabei. Bereits im Juli dieses Jahres wurden mit GB100-Chips und HBM-Bausteinen als Dummies mechanische Tests vorgenommen, die Grundlage war ein 110 × 110 mm großes Package. Im August sollen die Dummy-Chips dann durch funktionsfähige Lösungen wie 2 × GB102 plus HBM ersetzt werden. Hier folgen nun unzählige weitere Testreihen.

Ab Februar 2026 könnte im Idealfall die erste Rubin-Lösung GR100 in die Testreihen aufgenommen werden. Dann würde sich auch der Formfaktor ändern, das finale SXM8 (Server PCI Express Module 8) würde anvisiert werden, das PCB dafür bis zu 450 × 450 mm groß werden. Diese Lösung wäre erneut ein weiterer Testlauf für den nachfolgenden Chip, im Oktober 2026 würde GR150 den Platz einnehmen. POR dürfte in dem Fall für Power-On-Reset stehen, damit starten die Testchips erst einmal wie geplant. Danach dürfte das Testen aber erst einmal weitergehen. Nvidia schreibt deshalb, dass CoWoP parallel zu CoWoS laufen wird, hier noch kein Ersatz angestrebt ist.

Die Wahrscheinlichkeit, dass alles jedoch so schnell umgesetzt wird, ist jedoch relativ gering. Taiwanische Medien berichten, dass diese Lösung am Ende vielleicht eher etwas für günstigere AI-Chips sei, deshalb werde sie in China favorisiert. Dort wiederum hat man aber offiziell keinen Zugriff mehr auf CoWoS von TSMC. Nvidia Rubin Ultra wiederum wird wohl viel zu groß sein, um mit dieser Lösung als erstes auf solch eine neues Packaging-Verfahren zu setzen. Es könnte also eher etwas für Generationen danach sein, Stichwort Feynman & Co.

CoWoP:

— Jukan (@Jukanlosreve) July 30, 2025

A major US firm's Taiwan and Japan teams jointly believe that Nvidia's Rubin Ultra will not adopt CoWoP. Research from Japan's Ibiden indicates that the ABF substrate for Rubin Ultra is significantly larger and has more layers than that of the standard Rubin. It would be… https://t.co/INBs2esLkT