Next-Gen-Packaging: TSMC zu CoWoS, SoIC, SoW, HBM-Base-Dies, Optics und mehr

Packaging war ein weiteres wichtiges Thema auf TSMCs 2025 Symposium. CoWoS-L, SoIC Gen 3 und Neuheiten rücken in den Fokus. Denn für immer komplexere Arten an Chips werden auch stetige Verbesserungen nötig. Diese werden zusammen mit den passenden neuen Fabrikbauten realisiert.

TSMCs Packaging-Möglichkeiten im Überblick

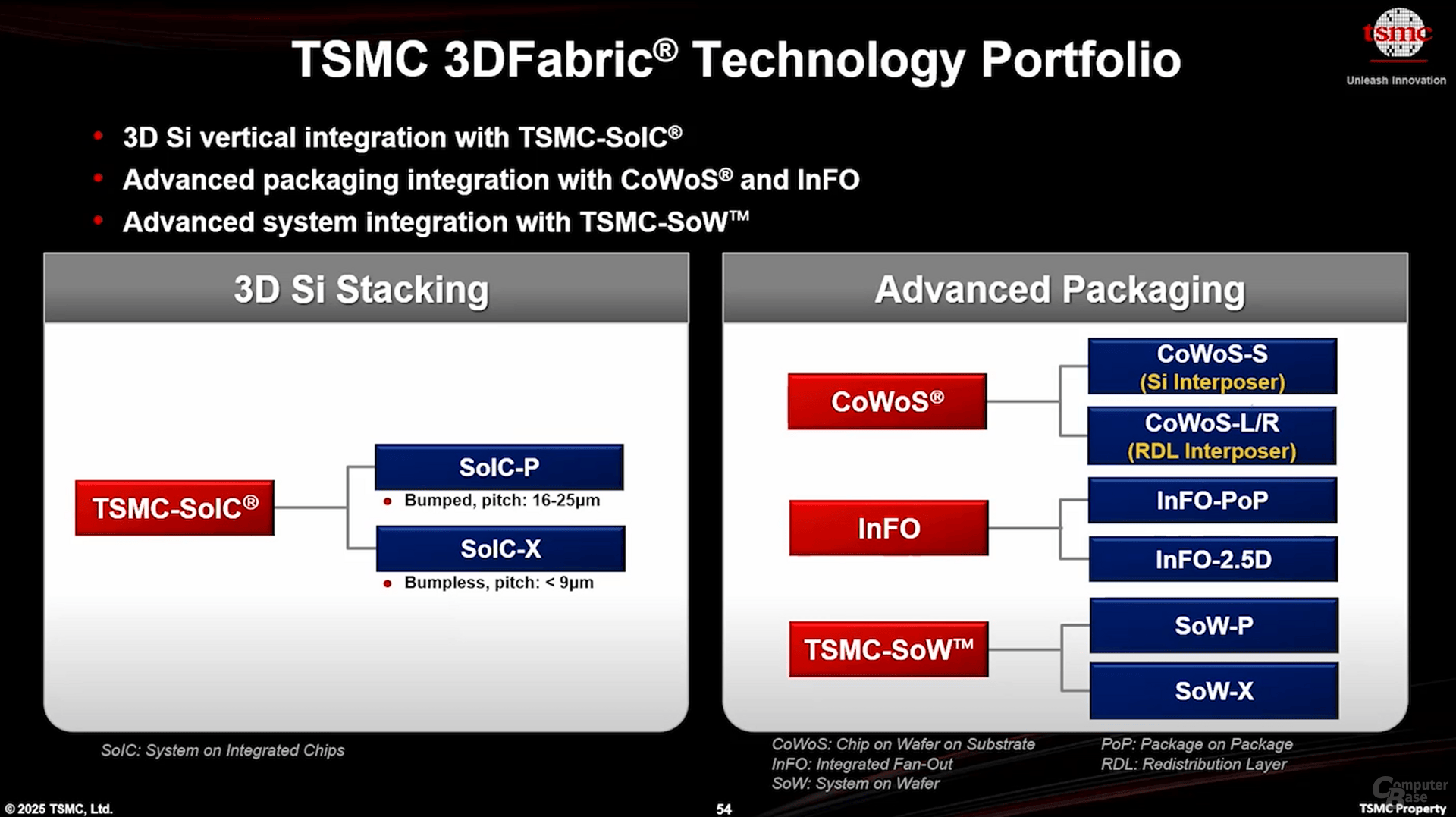

TSMC 3DFabric heißt der Oberbegriff über die Packaging-Möglichkeiten. Auf CoWoS-S und SoIC in der ersten Generation, sichtbar in Produkten wie Nvidia Hopper und AMD Ryzen X3D, übernehmen nun CoWoS-L, beispielsweise bereits für Nvidia Blackwell, und SoIC in der dritten Generation. InFO ist erfolgreich im Smartphone zu finden, hier gibt es gestapelte Lösungen bereits ebenfalls seit Jahren.

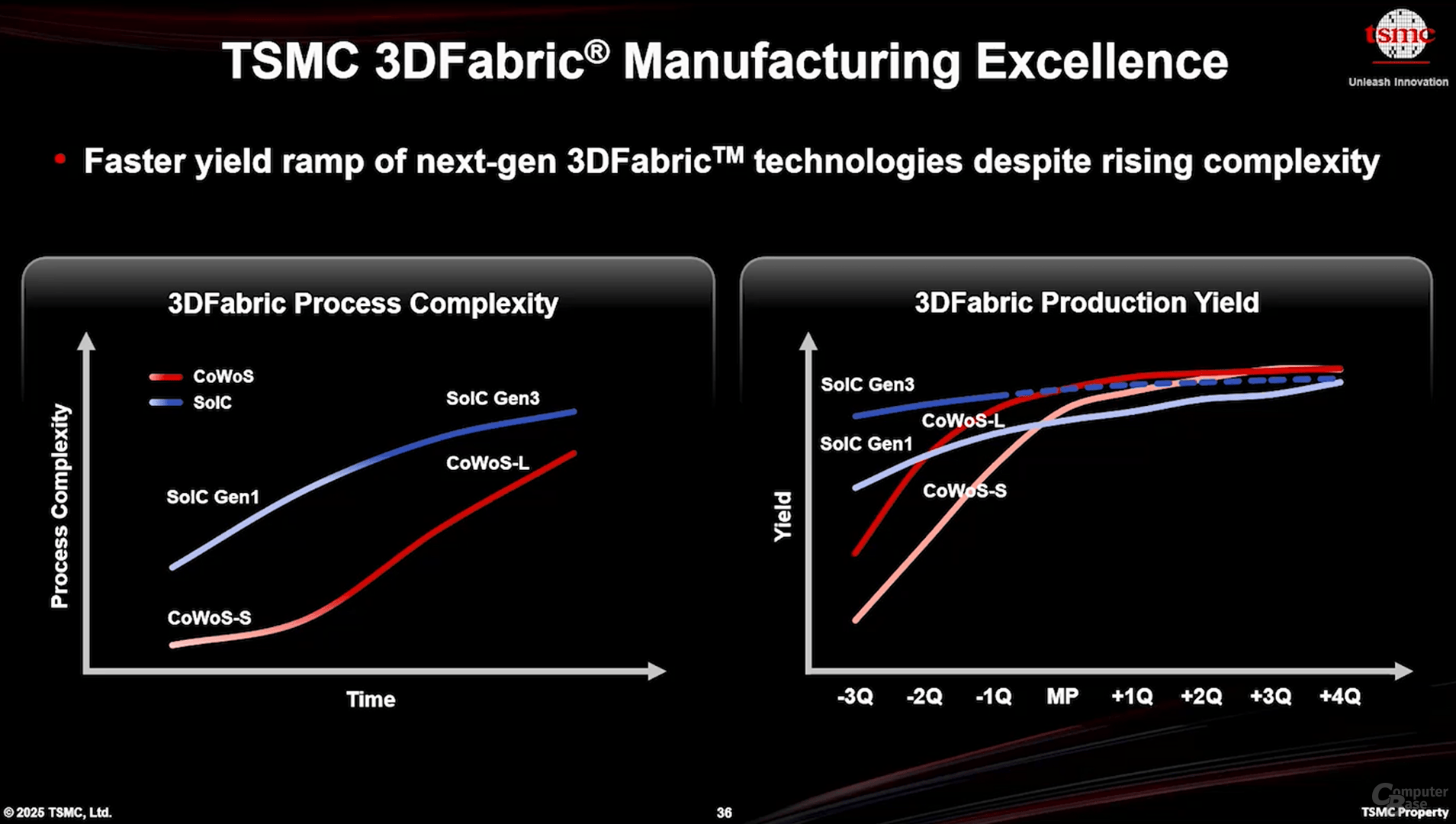

Die Lernkurve ist dabei deutlich steiler, viele Probleme der ersten Lösungen werden bei den neuen Varianten gleich zuvor gelöst. Das neue SoIC für Stacking von Chips, wie AMDs X3D-Cache auf den vorhandenen CCD, startet gleich bei der Ausbeute, in der die erste Generation unterwegs ist. Die Komplexität war und ist vor allem bei SoIC eine höhere, bei CoWoS werden in der Regel bekanntlich „nur“ die Chips nebeneinander auf einem Interposer gestapelt, bei SoIC hingegen mittels TSVs durchkontaktiert und dann übereinander gepackt.

Die Wachstumsraten in den jeweiligen Bereichen sind nach wie vor extrem. 100 Prozent pro Jahr hier, 80 Prozent pro Jahr dort, dies verdeutlicht einmal mehr, warum TSMC mit den Neubauten im Bereich Advanced Packaging nicht hinterherkommt und die zur Verfügung stehende Kapazität schon immer mindestens für das aktuelle und oft auch schon das kommende Jahr ausgebucht ist.

SoIC nimmt an Fahrt auf

SoIC (System on Integrated Chip) für das direkte Stapeln von Chips mittels TSV übereinander steht dabei aber sogar noch am Anfang. Hier sollen über die kommenden Jahre noch viele weitere Möglichkeiten geboten werden. In diesem Jahr startet die Produktion von N3-Chips gepaart mit gestapelten N4-Chips und erstmals dem sogenannten Face-to-Face-Verfahren mit deutlich verbessertem Interconnect, kleinerem Bump Pitch und größeren Reticle, nachdem es zuletzt noch N4-Chips mit gestapelten N5-Lösungen als Face-to-Back-Verfahren waren. Diese Schritte werden in den kommenden Jahren so fortgeführt, 2029 wird eine vollständige GAA-Lösung verfügbar sein, A14-Produkte und gestapelte N2-Chips dazu.

CoWoS ist und bleibt das Zugpferd für große Chips

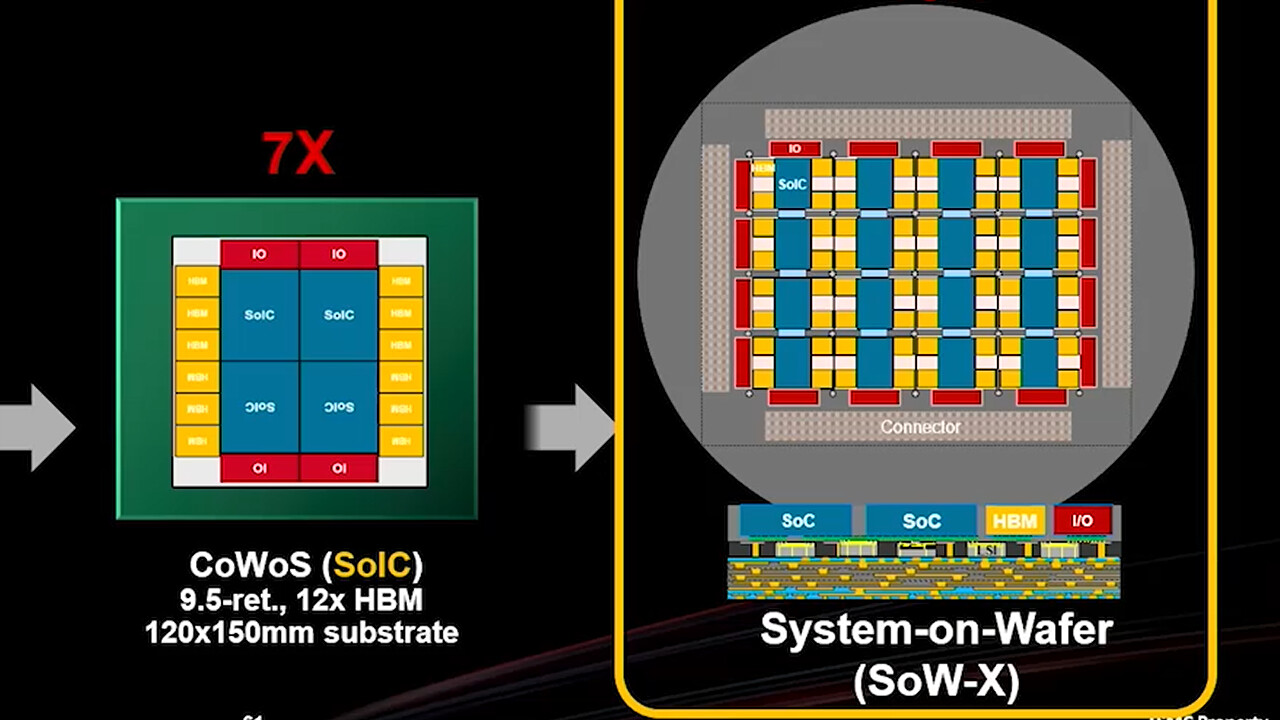

Seit 2021 bereits in Produktion, hat sich CoWoS (Chips on Wafer on Substrat) zum Kassenschlager entwickelt. Kein moderner größerer Chip ist ohne diese Technologie verfügbar. Von CoWoS-S verlagert sich das ganze in diesen Tagen zu CoWoS-L, das noch größere Chips erlauben wird. Bei CoWoS-S war bei der 3,3-fachen Größe der theoretischen Einzelchips auf einem Interposer das Limit erreicht, bei CoWoS-L wird dies unter anderem durch den viel größeren Interposer von 120 × 150 mm aber auch zusätzliche integrierte Features wie integrierte Voltage-Regulators (FIVR) nun schon einmal auf bis zu 9,5x Reticle gestreckt.

Als Reticle-Size-Limit in der Branche gilt die Maximalgröße eines einzelnen Chips, der mit gängigen Belichtungsmaschinen Kantenlängen von bis zu 26 × 33 mm bzw. 858 mm² haben kann. TSMC nutzt vereinfacht 830 mm² als maßgebendes Limit, denn vollkommen ausgereizt wird dies ungern. 9,5 mal 830 mm² entspricht einer Fläche von knapp 7.900 mm², der Interposer darunter bietet theoretisch 18.000 mm² Platz. Im Jahr 2027 können so zusammengepackte Riesenchips erscheinen, die mindestens vier bereits gestapelten SoIC-Chips flankiert von I/O und 12 HBM4E-Stacks beherbergen.

SoW – wenn ein Chip so groß wie ein Wafer wird

Und wenn selbst das nicht ausreicht, kommt System on Wafer (SoW) ins Spiel. Der erste Versuch ist bereits seit dem vergangenen Jahr in Produktion, Cerebras Waferscale-System ist hier das Aushängeschild. 2027 folgt mit SoW-X der nächste große Schritt, dann soll die Technologie die anderen vorhandenen Möglichkeiten auf Wafer-Ebene hochskalieren können.

Noch mehr Technologie ins Package packen

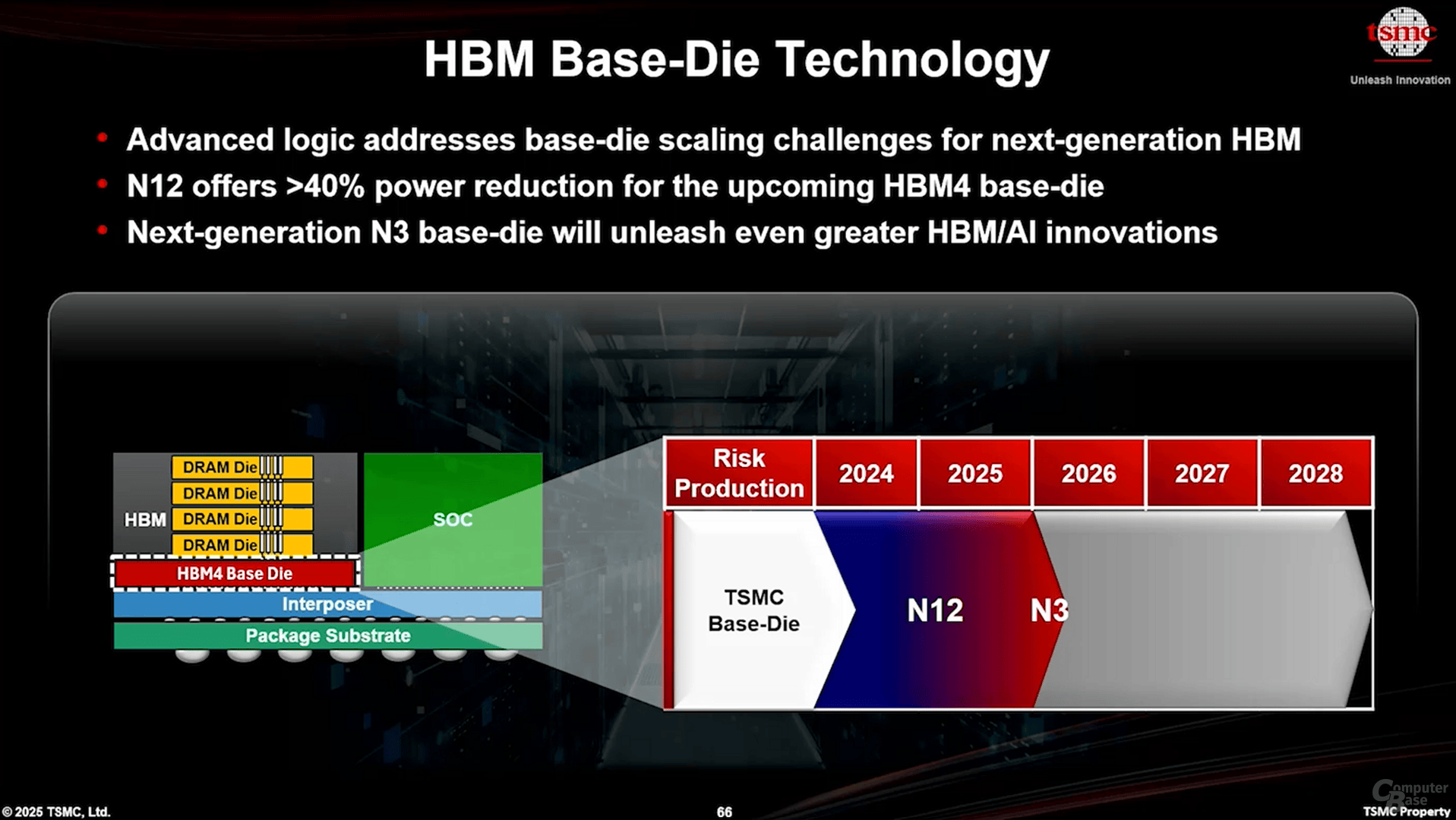

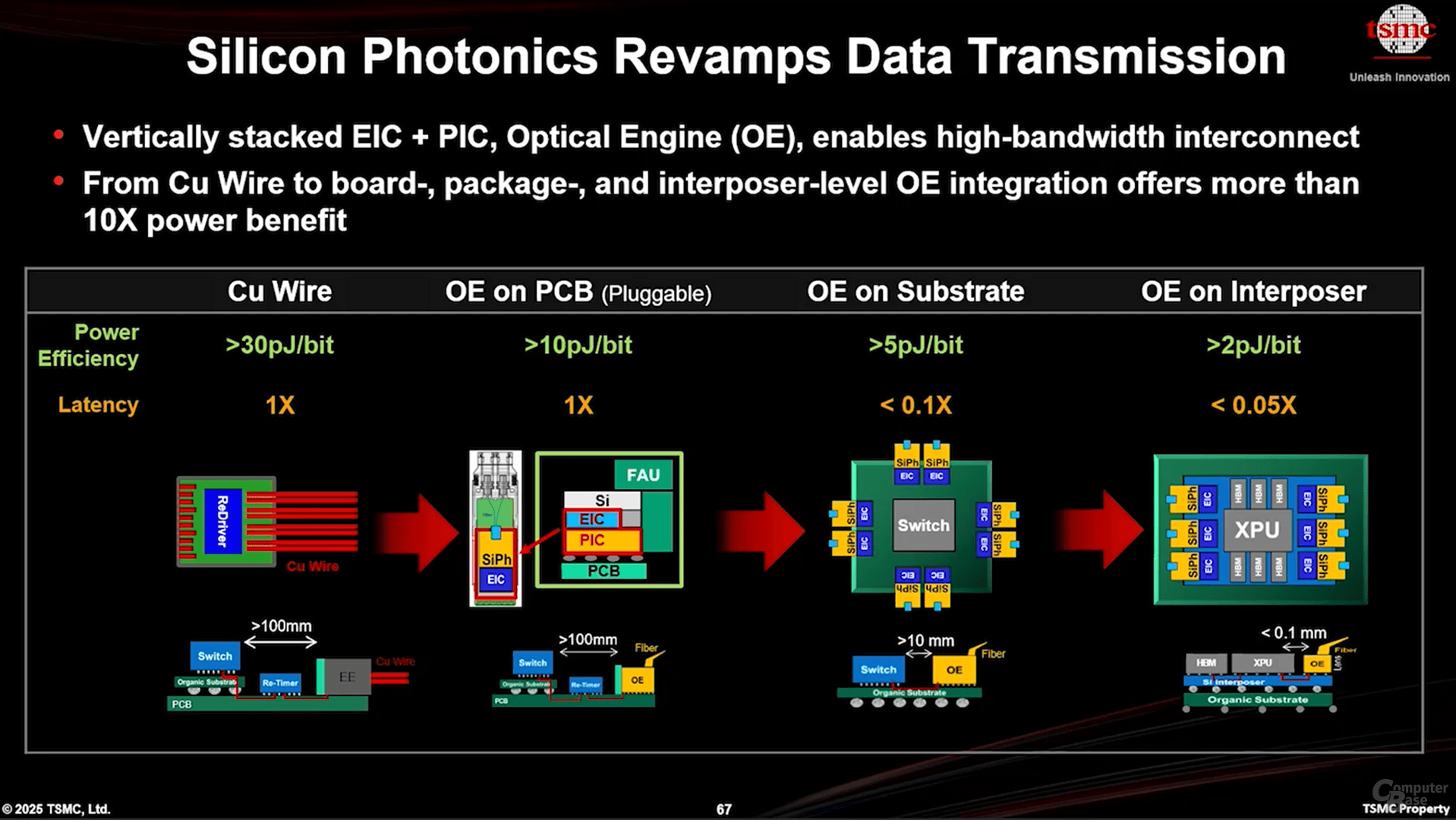

Die Stromversorgung und optische Datenverbindungen sind ebenfalls ein Thema bei TSMC. Zum Teil integrierte Schaltungen sollen die Effizienz deutlich steigern, moderne Fertigungsprozesse einen weiteren Teil dazu beitragen. Moderne Base-Dies helfen beispielsweise HBM dabei, Strom zu sparen. Optische Datenverbindungen werden nicht nur hinsichtlich der Leistungsfähigkeit optimiert, vor allem wird auch ihr Strombedarf gesenkt, bisher ein großes Hindernis bei der Skalierung.

Viele der genannten Möglichkeiten werden in Zukunft nicht auf Server, PCs, Kommunikationssysteme und Smartphones beschränkt bleiben, sondern in alle Richtungen ausgeweitet. Automotive ist ein ganz großes Thema, aber auch Robotics hat TSMC im Blick. Chips, gefertigt von TSMC mit aktuell 24 Fabriken im Bau, sind im Alltag heute schon fast, aber spätestens dann nahezu überall zu finden.