Hast du denn genug Anwendungen die damit skalieren?drago-museweni schrieb:Freue mich voll auf Zen6, entweder entspannt 12 Kerne oder dezent auf 24 Wechseln und wenn die Gerüchte stimmen auf allen Kernen 3D Cache.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

Du solltest ein Upgrade durchführen oder einen alternativen Browser verwenden.

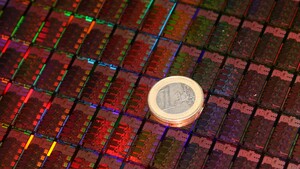

News Epyc „Venice“ delidded: Nackte Zen-6-CPU dürfte auch die Zukunft von Ryzen zeigen

foofoobar

Rear Admiral

- Registriert

- Dez. 2011

- Beiträge

- 5.331

Hat Intel mittlerweile einen brauchbaren Interconnect bzw. Fabric?ZeroCoolRiddler schrieb:Aber ja, sind schon echte Monster. Monolitisch wäre das überhaupt nicht machbar oder ein finanzielles Desaster. Jetzt zahlt sich die Investition in die Chiplet Geschichte erst richtig aus.

Oder gammelt Intel immer noch mit Ringbus durch die Gegend?

heroesgaming

Commander

- Registriert

- Feb. 2022

- Beiträge

- 2.930

Danke für den Link. Mit Strix Halo habe ich mich ehrlicherweise nicht wirklich auseinandergesetzt, aber ganz klar zeigt dieses Produkt, was für ein Potenzial AMD da für seine großen CPUs noch abzuschöpfen hat. Kein Wunder, dass auch Intel mit Nova Lake in die Vollen zu gehen scheint, was Kerne und Cache angeht.stefan92x schrieb:Ich verweise immer gerne auf diesen Test: https://www.phoronix.com/review/ryzen-ai-max-395-9950x-9950x3d/11

"The AMD Ryzen AI Max+ 395 being able to deliver 95% the performance of the Ryzen 9 9950X overall for CPU-based workloads while consuming just 59% the power on average is quite impressive"

Kombiniert mit besserer Fertigung und Architektur dürften da für solche Nutzungsszenarien wie in dem Benchmark die gleiche Leistung bei halbem Verbrauch realistisch werden, wenn nicht sogar eher noch besser.

foofoobar

Rear Admiral

- Registriert

- Dez. 2011

- Beiträge

- 5.331

LPDDR säuft auch weniger als DDR.stefan92x schrieb:Kombiniert mit besserer Fertigung und Architektur dürften da für solche Nutzungsszenarien wie in dem Benchmark die gleiche Leistung bei halbem Verbrauch realistisch werden, wenn nicht sogar eher noch besser.

- Registriert

- Juli 2021

- Beiträge

- 1.350

Extrem gespannt darauf, welche CPU denn die ultimative neue Gaming-CPU sein wird. Ein 10800X und später gefolgt vom 10800X3D?

Stimmt. Andererseits hängt bei Strix Halo auch noch eine fette iGPU mit im Chip und er hat mehr Speicherkanäle, andererseits hat der normale Ryzen auch noch mehr IO etc... es ist kein 1:1 Vergleich, aber es zeigt eine grobe Richtung an.foofoobar schrieb:LPDDR säuft auch weniger als DDR.

- Registriert

- Okt. 2006

- Beiträge

- 7.372

@foofoobar

Intel? Verfolge ich seit Jahren nicht mehr.

Intel? Verfolge ich seit Jahren nicht mehr.

Was meinst Du was AMD intern hat? Ringbus, hier Ringbus da.foofoobar schrieb:Oder gammelt Intel immer noch mit Ringbus durch die Gegend?

Botcruscher

Commodore

- Registriert

- Aug. 2005

- Beiträge

- 4.924

mm² wären interessant.

heroesgaming

Commander

- Registriert

- Feb. 2022

- Beiträge

- 2.930

Der Ringbus war ja schon immer ein Intel-Ding, das sie ja immerhin seit dem ersten Core i7 (?) im Einsatz haben. Da wird er sich schon nicht verschrieben haben ^_^ETI1120 schrieb:Was meinst Du was AMD intern hat? Ringbus, hier Ringbus da.

@heroesgaming Im Server war Intel aber auch viel mit Mesh-Designs statt mit Ringbus unterwegs.

Eigentlich hat AMD von der Topologie her viel mehr auf Ringe gesetzt als Intel

Eigentlich hat AMD von der Topologie her viel mehr auf Ringe gesetzt als Intel

- Registriert

- Apr. 2005

- Beiträge

- 2.334

Leicht erkennbar und im Titel darunter auch korrekt durchgezählt, dass es dann doch eher acht sindLeicht erkennbar sind die jeweils sechs HBM4-Chips an der Außenseite, in der Mitte sitzen die ebenfalls direkt miteinander verbundenen GPU-Chiplets.

Oder AMD wechselt auf römische Ziffern, wie schon Mal bei den früheren Radeons (als es noch Ati war) gemacht wurde. Nach 9000er Reihe folgte da ein X als erste Ziffer, also X600, X800 usw. statt 10600 und 10800. Danach kam dann die X1xxx Reihe bei den Radeons. Die 10000er Ryzen könnten also entsprechend Xxxx heiß und danach dann X1xxx, X2xxx usw.Schlumpfbert schrieb:Für den Desktop werden die nächsten Namen doch eher 11000 als 10000?

1000

2000 (Ausnahme)

3000

5000

7000

9000

?

das auch, aber deshalb ist das Foto von Venice schief, damit man nicht die Chiplets vom Sockel ausmessen kann.Botcruscher schrieb:mm² wären interessant.

Aber was ist das?

auch auf der anderen Seite sind 4 chiplets, dummy silizium würde man doch nicht 4 teilen?

foofoobar

Rear Admiral

- Registriert

- Dez. 2011

- Beiträge

- 5.331

Aber eben nicht über verschiedene Dies.ETI1120 schrieb:Was meinst Du was AMD intern hat? Ringbus, hier Ringbus da.

Evtl. Phys?ETI1120 schrieb:das auch, aber deshalb ist das Foto von Venice schief, damit man nicht die Chiplets vom Sockel ausmessen kann.

Aber was ist das?

Mesh4Chiplets? Smells strange.stefan92x schrieb:@heroesgaming Im Server war Intel aber auch viel mit Mesh-Designs statt mit Ringbus unterwegs.

Die Architektur von AMD kann man als hierachical Ring beschreiben. Ein Ring im CCX und ein Ring im IOD bzw. SoC.stefan92x schrieb:@heroesgaming Im Server war Intel aber auch viel mit Mesh-Designs statt mit Ringbus unterwegs.

Eigentlich hat AMD von der Topologie her viel mehr auf Ringe gesetzt als Intel

Und nun wird es spanend was AMD bei 32 Core CCX gemacht hat "Mesh" wie einige behaupten oder wieder als hierarchical Ring

Sehr spannend...ETI1120 schrieb:Aber was ist das?

Gut möglich, denn vielleicht muss ich meinen Kommentar von Seite 1 doch revidieren, in dem ich sagte, dass ein aneinanderreihen von mehreren IODs nicht geht.foofoobar schrieb:Evtl. Phys?

Vielleicht war AMD wieder ganz stumpf und verwendet für die Kopplung der IOD PCIe-Interfaces ohne PHYs. Dann wären beide IODs ganz simpel identisch, und für die Verbindungen nach außen flanscht man extra PHY-Chiplets dran.

Würde dann auch sehr elegant kleinere Varianten mit nur einem IOD ermöglichen, statt einen zweiten IOD anzubinden, baut man auch auf die Seite PHYs im Packaging ein.

@ZFS ich nehme also alles zurück und behaupte das Gegenteil

CDLABSRadonP...

Vice Admiral

- Registriert

- Feb. 2021

- Beiträge

- 6.865

Ich tippe auf Ryzen AI 500, denn OlympicRidge wird sicherlich eine NPU tragen.stefan92x schrieb:Bislang hat AMD es so gehandhabt, dass jedes Jahr eine Ryzen-Serie rauskam, aber manchmal nur Desktop-CPUs (1000, 3000, 7000, 9000) manchmal nur APUs (4000, 6000, 8000), und manchmal auch beides (2000, 5000). Allerdings gibt es keine Ryzen 10000, stattdessen heißen die APUs jetzt Ryzen AI 300/400. Damit ist ein bisschen unklar, wie AMD weiter zählen wird.

Bei Venice muss AMD den Ringbus im IOD zweiteilen.foofoobar schrieb:Aber eben nicht über verschiedene Dies.

Anonsten waren bisher die Ringbusse auf einem Die aber die Verbindungen zwischen den Ringen gingen über das Substrat.

War auch meine erste Idee, aber welche?foofoobar schrieb:Evtl. Phys?

Ähnliche Themen

- Antworten

- 113

- Aufrufe

- 9.926

- Antworten

- 93

- Aufrufe

- 6.265