Matthiazy schrieb:

Dort steht für das Jahr 2027 der Sockel AM6 mit Zen7.

IMO ist Zen 7 im Jahr 2027 sehr unrealistisch, insbesondere was den Desktop anbelangt.

Erst Mal zu Zen 6. AMD hat sich heute nicht herabgelassen etwas zum Zeitpunktes des Releases von Venice zu sagen. Viele Gerüchte besagen Venice kommt vor Olympic Ridge. Ich halte dies inzwischen für realistisch.

Die meisten Gerüchte gehen bei Zen 7 von 2028 aus und viele sagen AMD bleibt mit Zen 7 auf AM5.

Matthiazy schrieb:

Es sei den AM6 unterstützt DDR5 UND DDR6 SDRAM so wie Alder-Lake mit DDR4 und DDR5.

Bei Alder Lake mussten sich Käufer sich beim Kauf des Boards entscheiden, welchen Speicherstandard sie verwenden wollen. Raptor Lake war eigentlich ein Alder Lake Refresh. Der richtige Nachfolger Arrow Lake ist auf einer neuen Plattform erschienen und unterstützt nur DDR5.

Zwei Speicherstandards ergibt für eine kurzlebige Plattform Sinn, wenn sie genau in der Übergangzeit released wird.

Zwei Speicherstandards in einer langlebigen Plattform zu unterstützen, bedeutet beide Standards in allen SoCs-Generationen zu unterstützen. Wenn der alte Speicherstandard nur in der ersten Generation der SoCs unterstützt wird, dass ist die neue Plattform eben nur halb langlebig. Halbe Sachen, ...

Matthiazy schrieb:

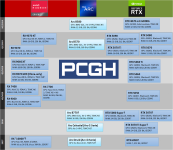

Es sind nun Mal schon lange überholte Informationen. Das sieht man alleine schon der Platzierung von 9000G

Es wäre längst an der Zeit gewesen diese veralteten Grafik zu ersetzen ...

Matthiazy schrieb:

Das auf den Bildern ist nur bekannt.

... allerdings waren diese Grafiken waren schon immer wilde Spekulation.

Die Informationen zu Zen 7 haben noch nie gepasst. 14A ist ein Intel Node. TSMC A14 steht für 2028 auf der TSMC Roadmap. Damit ist es völlig ausgeschlossen dass noch 2027 und bis Mitte 2028 Produkte mit TSMC A14 erscheinen. Wenn es so wie bei N3 und N2 läuft kommen die ersten Produkte mit TSMC A14 sogar erst 2029. Das wurde MLID schon um die Ohren gehauen, als das Video lief.

MLID hat übrigens sehr schnell nachgeschoben, dass Zen 7 noch auf AM5 kommt.

---

Roadmap von SK Hynix, die Du auch kennst, ordnet DDR6 in den Zeitraum 2029 bis 2031 ein. Das ist ein Zeitraum von 3 Jahren! Bezieht sich SK Hynix auf die ersten Produkte oder darauf dass DDR6 SDRAM Mainstream ist. Also für mich besagt diese Roadmap nur dass DDR6 die nächsten Jahre kein Thema ist.

Es ist offensichtlich, dass sich die Pläne der JEDEC zu DDR6 SDRAM geändert haben. Der früher Mal genannte Termin Q2 2025 ist schon lange verstrichen und es gibt keine Anzeichen dass der DDR6 Standard in absehbarer Zeit kommt. Was sehr gut zu der Roadmap von SK Hynix passt.

Und ganz kurz ins eingemachte:

DRAM skaliert praktisch nicht mehr und es ist offensichtlich, dass in absehbarar 2D DRAM abgelöst werden muss. Allerdings ist heute unklar was 2D DRAM ablösen wird.

Selbst wenn es 3D DRAM werden sollte hätte dies weitreichende Auswirkungen auf die organisation der Dies und damit darauf wie das DRAM an die Processing Units angebunden wird. AFAIU ist man sich heute nicht Mal sicher, ob die Kondensatoren vertikal (wie bisher) oder horizontal anordnen soll.

Wenn es eine Non-Volantile Speicherzelle werden sollte, hätte es massive Auswirkungen für die Computersysteme.

Nun kommen wir zur Kaffesatzlesersei, ohne jede Gewähr:

- Wenn DDR6 SDRAM auf den bisherigen 2D Speicherzellen basiert, dann ist DDR6 SDRAM sehr wahrscheinlich bis 2030 Mainstream. Also rechtzeitig für Zen 8.

Allerdings wird zu diesem Zeitpunkt schon ziemlich klar sein, wie es bei Hauptspecher weitergeht, und es besteht die Möglichkeit, dass DDR6 SDRAM schon beim Erscheinen als veralteter Kram gilt

- Wenn DDR6 SDRAM auf den 3D Speicherzellen basiert, wird DDR6 SDRAM erst nach 2030 relevant.

Matthiazy schrieb:

Ob es wirklich so passieren wird sieht man erst in paar Jahren.

Die Grafik ist was die AMD CPUs betrifft falsch.